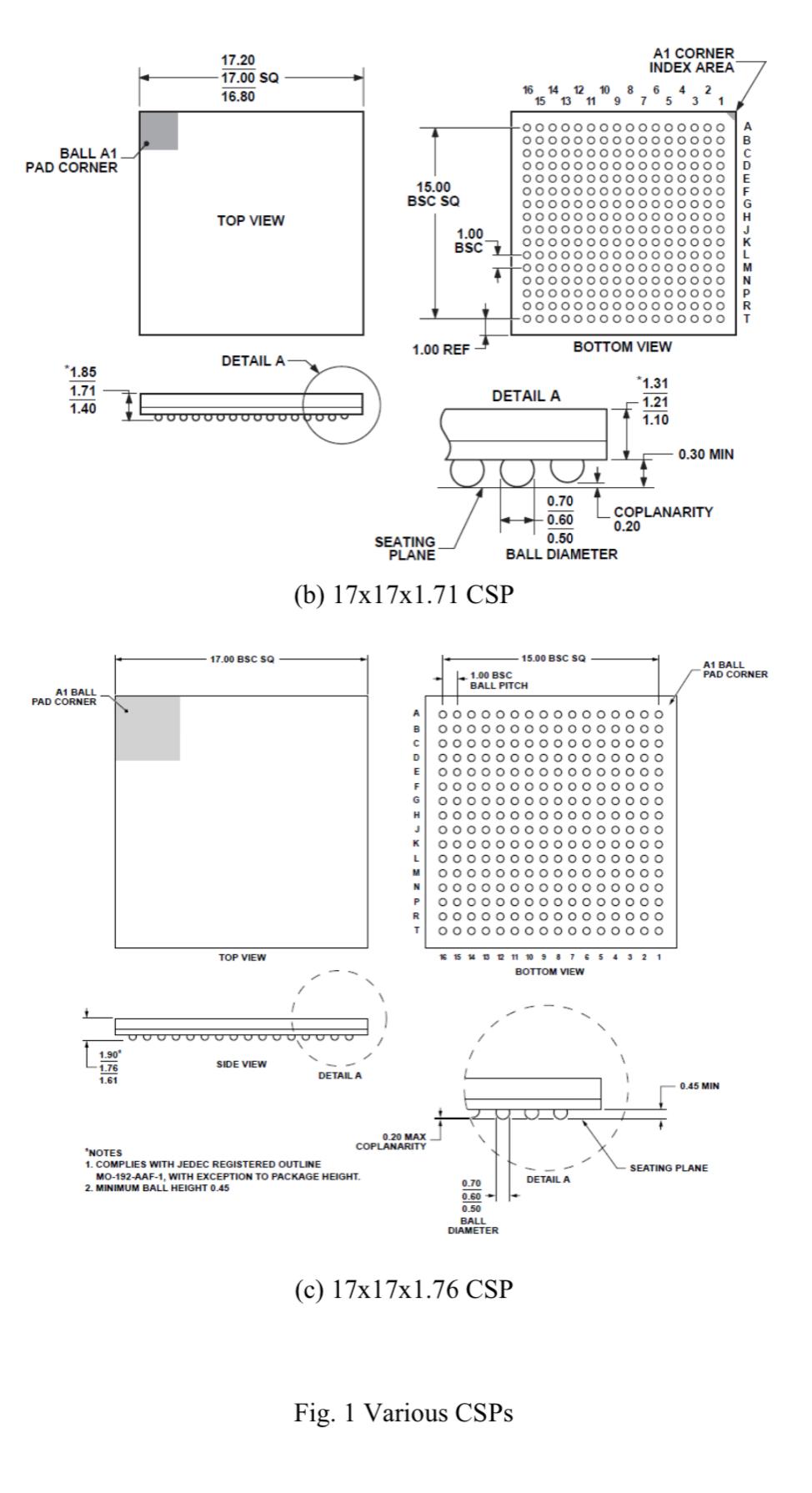

Figure 1 from Development of a Low CTE chip scale package

$ 118.99

-

By A Mystery Man Writer

-

-

4.7(665)

Product Description

Figure 1. CSP on Test Card - "Development of a Low CTE chip scale package"

Table 1 from Ultra low CTE (1.8 ppm/°C) core material for next

Experimental and Numerical Investigation of Delamination Between

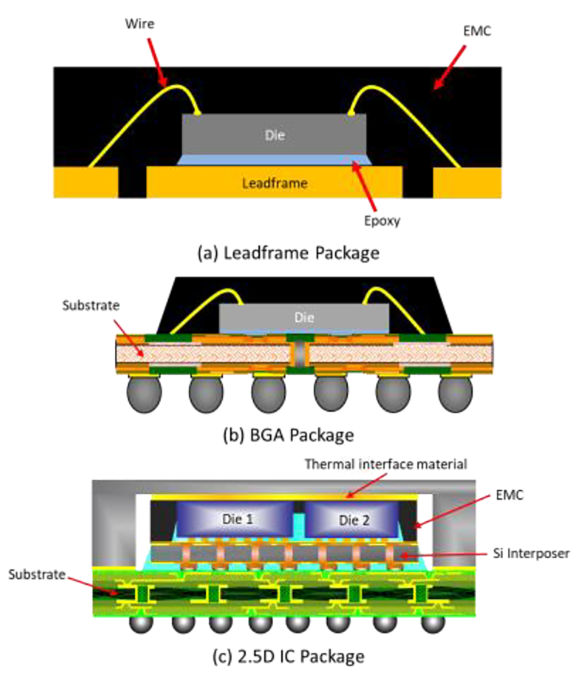

Figure 1 from Development of a Low CTE chip scale package

Polymers, Free Full-Text

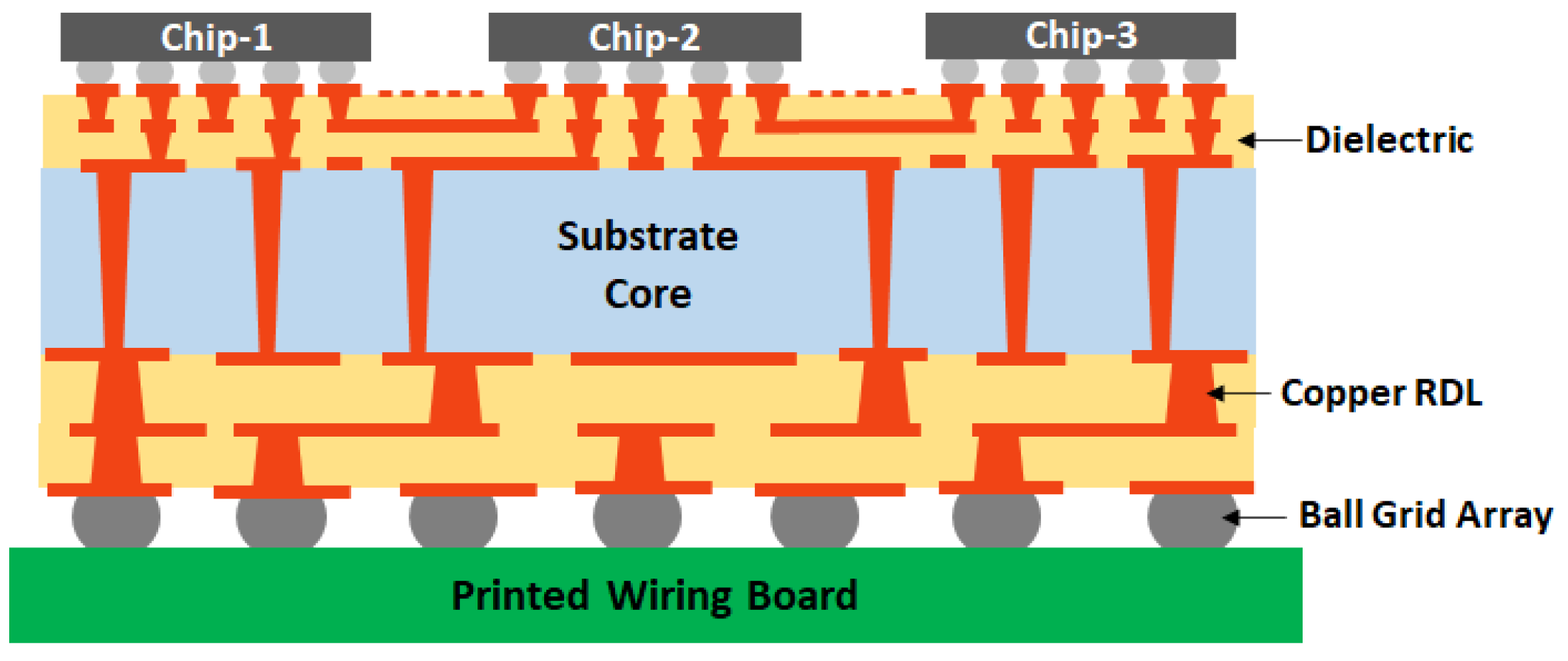

Solved Consider Chip Scale Packages (CSP) assembled on to a

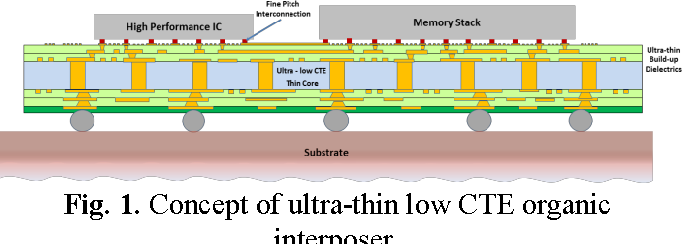

Figure 1 from Modeling, design and fabrication of ultra-thin and

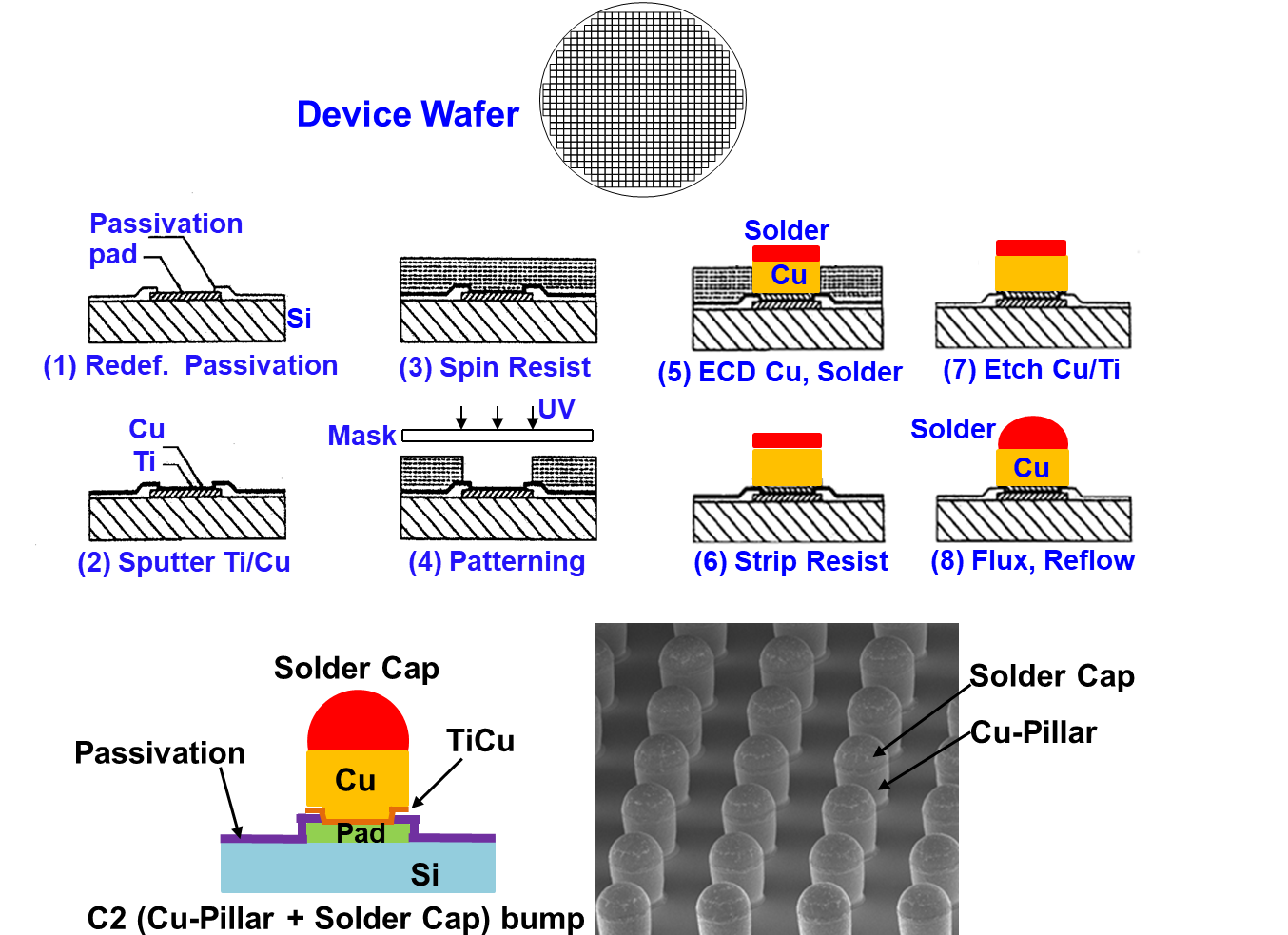

Scaling Bump Pitches In Advanced Packaging

Hot Trends In Semiconductor Thermal Management

Chip Scale Packages - an overview